# ST7548

# PCMCIA AND PC GENERAL PURPOSE INTERFACE

#### ADVANCE DATA

- PCMCIA AND PC GENERAL PURPOSE IN-TERFACE (MODEM, ISDN, MULTIMEDIA)

- ExCA<sup>TM</sup> COMPATIBLE (see Note 1)

- 494 BYTES INTERNAL RAM WITH BUS AR-BITRATION

- PCMCIA CONFIGURATION REGISTERS (R0, R1)

- CONFIGURABLE I/O DECODER

- I<sup>2</sup>C EEPROM INTERFACE (256 BYTES)

- 16C450 UART WITH 16 WORDS FIFO ON DATA

- CONFIGURABLE CLOCK GENERATOR

- I/O MCU MEMORY EXTENSION 8 BITS PORT

- HIGH THROUGHPUT :

- 115200bpsTHROUGH UART

- 2MBYTES THROUGH RAM

- 3.3V OR 5V SUPPLY (±10%)

- LOW POWER

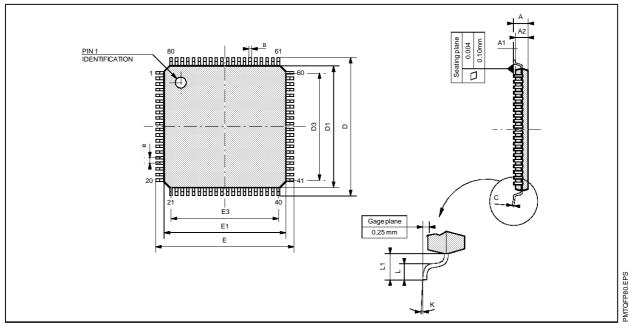

- SMALL OUTLINE TQFP80 PACKAGE

- ALSO AVAILABLE WITH COMPLETE MO-DEM CHIP SET

#### **GENERAL DESCRIPTION**

The ST7548 is a flexible interface for the PCMCIA and PC buses mainly dedicated to telecommunications. It is fully in accordance with PCMCIA standard and is designed to be coupled to a modem. It includes a UART, a 494 bytes internal memory, an  $I^2C$  interface allowing chip initialization from an external EEPROM, and a programmable clock generator.

It also includes a configurable port which can be used either as I/O or memory extension or as an interface to a wide range of microprocessors. In this case, using the internal memory, high speed data transfers can be achieved between the PC and the application.

It is realised in an ultra-flat TQFP80 package suitable for PCMCIA cards.

Note: 1. ExCa is a trademark of Intel Corporation.

March 1996

This is advance information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

## ST7548

| CONTE                                | NTS                                                                                                                                                                                           | Page                 |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| I                                    | PIN CONNECTIONS.                                                                                                                                                                              | 4                    |

| II                                   | PIN DESCRIPTION.                                                                                                                                                                              | 5                    |

| ш                                    | BLOCK DIAGRAM                                                                                                                                                                                 | 8                    |

| IV                                   | FUNCTIONNAL DESCRIPTION                                                                                                                                                                       | 9                    |

| IV.1                                 | PCMCIA ADDRESSING MODES                                                                                                                                                                       | 9                    |

| IV.2                                 | CLOCKS                                                                                                                                                                                        | 10                   |

| IV.3                                 | UART                                                                                                                                                                                          | 11                   |

| IV.4                                 | I <sup>2</sup> C LINE INTERFACE                                                                                                                                                               | 12                   |

| IV.4.1<br>IV.4.2<br>IV.4.3           | Introduction<br>State Machine Behaviour<br>Sequential Random Read Protocol                                                                                                                    | 12<br>12<br>13       |

| IV.4.4                               | Byte Write Protocol                                                                                                                                                                           | 13                   |

| IV.5                                 | BUS ARBITRATION                                                                                                                                                                               | 13                   |

| IV.6                                 | REGISTERS                                                                                                                                                                                     | 14                   |

| IV.6.1<br>IV.6.2<br>IV.6.3<br>IV.6.4 | CONTROL PC (8 Bits, Address X"1EE", R/W).<br>CONTROL MCU (8 Bits, Address X"1EE", R/W).<br>CONFIGURATION_STATUS (8 Bits, Address X"1EF").<br>R0 (8 Bits, Address X"1F0", R/W).                | 14<br>14<br>14<br>15 |

| IV.6.5<br>IV.6.6<br>IV.6.7           | R1 (8 Bits, Address X"1F2", R/W).         ADRDEC (8 Bits, Address X"1F4", R/W)         MASK (8 Bits, Address X"1F6", R/W).                                                                    | 16<br>16<br>16       |

| IV.6.8                               | PROGN (8 Bits, Address X"1F8", R/W)                                                                                                                                                           | 17                   |

| IV.7                                 | RAM                                                                                                                                                                                           | 17                   |

| IV.8                                 | I/O - MCU - MEMORY EXTENSION MULTI-PURPOSE PORT                                                                                                                                               | 17                   |

| IV.8.1<br>IV.8.2                     | IntroductionI/O Port                                                                                                                                                                          | 17<br>18             |

| IV.8.3<br>IV.8.4                     | MCU Port                                                                                                                                                                                      | 18<br>18             |

| IV.9                                 | ADDRESSES CORRESPONDENCE                                                                                                                                                                      | 19                   |

| IV.9.1<br>IV.9.2<br>IV.9.3<br>IV.9.4 | Addresses Correspondence in Attribute Memory Mode         Addresses Correspondence in Common Memory         Address Correspondence in I/O Memory Mode         How to Dump a CIS in the EEPROM | 19<br>20<br>20<br>20 |

| IV.10                                | INTERRUPTS                                                                                                                                                                                    | 22                   |

| IV.10.1<br>IV.10.2                   | INTERRUPTS TOWARDS THE PC                                                                                                                                                                     | 22<br>22             |

| IV.11                                | ADDRESSING CAPABILITIES TABLE                                                                                                                                                                 | 23                   |

| v                                    | ABSOLUTE MAXIMUM RATINGS AND OPERATING VALUES                                                                                                                                                 | 24                   |

| VI                                   | DIGITAL INTERFACE                                                                                                                                                                             | 24                   |

| VII                                  |                                                                                                                                                                                               | 24                   |

| VIII                                 | POWER CONSUMPTION AND SUPPLY VOLTAGE RANGE                                                                                                                                                    | 24                   |

| CONTE            | ENTS (continued)                                  | Page     |

|------------------|---------------------------------------------------|----------|

| IX               | TIMING CHARACTERISTICS                            | 25       |

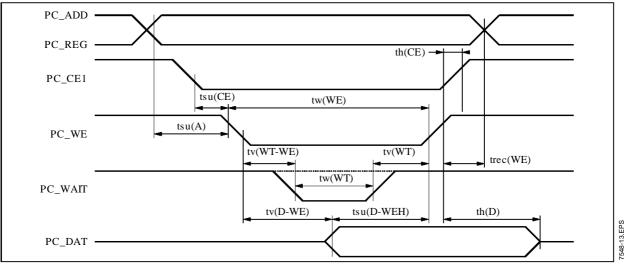

| IX.1             | PCMCIA BUS TIMING (COMMON MEMORY CYCLE)           | 25       |

| IX.2             | PCMCIA BUS TIMING (ATTRIBUTE MEMORY CYCLE)        | 26       |

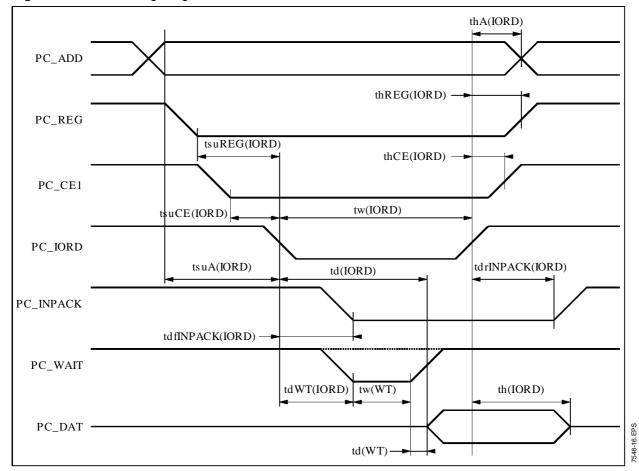

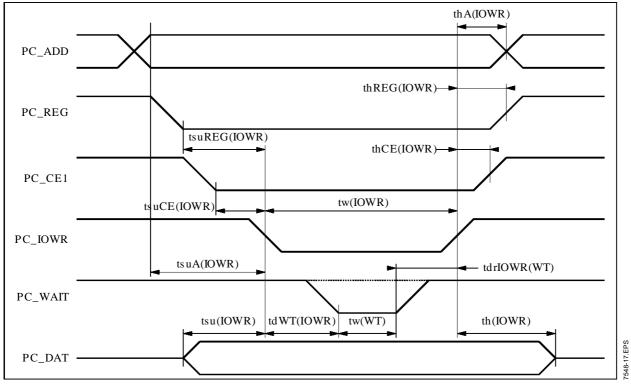

| IX.3             | PCMCIA BUS TIMING (I/O CYCLE).                    | 28       |

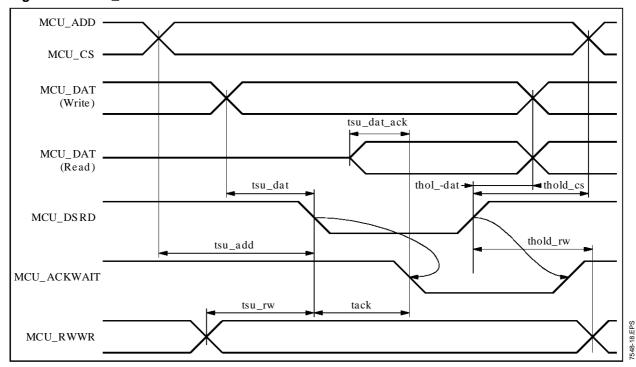

| IX.4             | MCU BUS TIMING                                    | 30       |

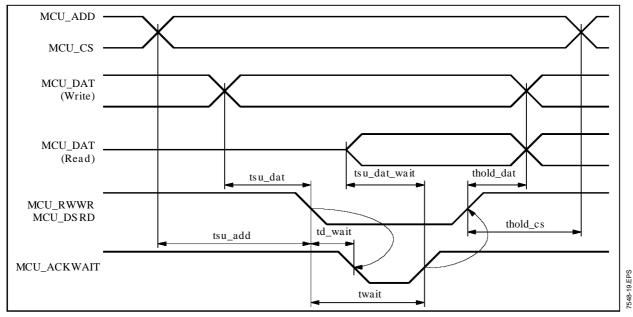

| IX.4.1           | Motorola, not multiplexed                         | 30       |

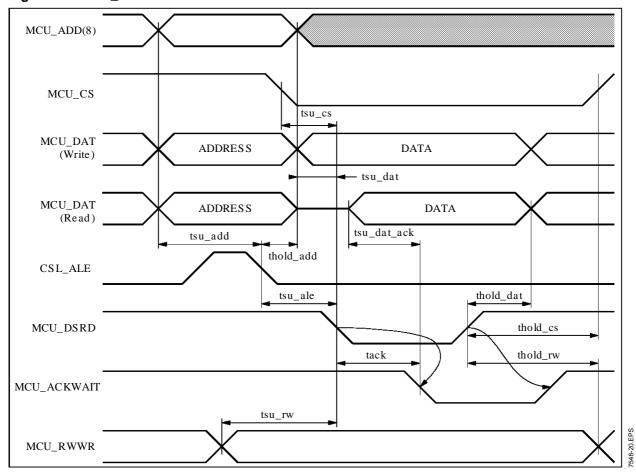

| IX.4.2           | Intel, not multiplexed.                           | 31       |

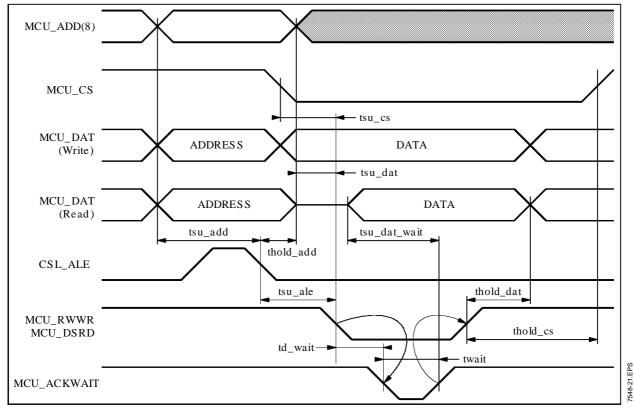

| IX.4.3<br>IX.4.4 | Motorola, multiplexed                             | 32<br>33 |

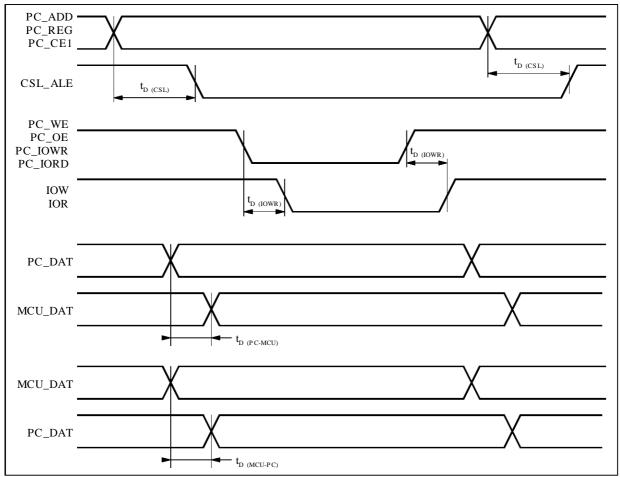

| IX.5             | Memory Extension and IO Extension Transfer Timing | 34       |

| IX.6             | I <sup>2</sup> C BUS TIMING.                      | 35       |

| X                | APPLICATIONS                                      | 36       |

| X.1              |                                                   | 36       |

| X.2              | MCU CONNECTION                                    | 36       |

| X.2.1            | Wiring                                            | 36       |

| X.2.2            | Polling.                                          | 36       |

| X.2.3            |                                                   | 36       |

| X.3              | UART USE                                          | 37       |

| X.4              | I/O EXTENSION                                     | 37       |

| X.4.1<br>X.4.2   | Wiring                                            | 37<br>37 |

| л.4.2<br>X.5     |                                                   | 38       |

|                  |                                                   |          |

| X.5.1<br>X.5.2   | Wiring   Operation                                | 38<br>38 |

| XI               | PACKAGE MECHANICAL DATA                           | 39       |

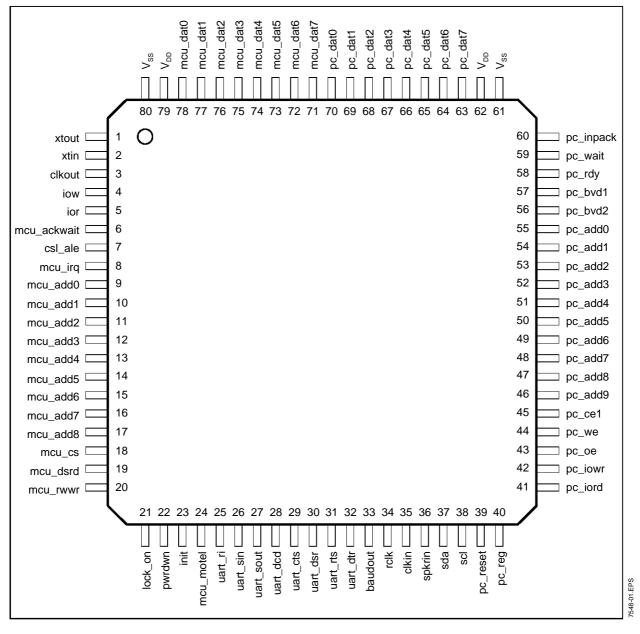

#### **I - PIN CONNECTIONS**

## **II - PIN DESCRIPTION**

| Name             | Pin                                                          | Туре       | Function                                                                                                                                                                                                                                                                                                                                                                |  |  |

|------------------|--------------------------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| POWER PINS (AL   | POWER PINS (ALL THE POWER AND GROUND PINS MUST BE CONNECTED) |            |                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| V <sub>DD1</sub> | 62                                                           | Power      | DC Supply                                                                                                                                                                                                                                                                                                                                                               |  |  |

| V <sub>DD2</sub> | 79                                                           | Power      | DC Supply                                                                                                                                                                                                                                                                                                                                                               |  |  |

| V <sub>SS1</sub> | 61                                                           | Ground     | DC Ground                                                                                                                                                                                                                                                                                                                                                               |  |  |

| V <sub>SS2</sub> | 80                                                           | Ground     | DC Ground                                                                                                                                                                                                                                                                                                                                                               |  |  |

| PC address bus   |                                                              | •          |                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| PC_ADD_0         | 55                                                           | I          | PCMCIA Address Bus Bit 0 (LSB)                                                                                                                                                                                                                                                                                                                                          |  |  |

| PC_ADD_1         | 54                                                           | I          | PCMCIA Address Bus Bit 1                                                                                                                                                                                                                                                                                                                                                |  |  |

| PC_ADD_2         | 53                                                           | I          | PCMCIA Address Bus Bit 2                                                                                                                                                                                                                                                                                                                                                |  |  |

| PC_ADD_3         | 52                                                           | I          | PCMCIA Address Bus Bit 3                                                                                                                                                                                                                                                                                                                                                |  |  |

| PC_ADD_4         | 51                                                           | I          | PCMCIA Address Bus Bit 4                                                                                                                                                                                                                                                                                                                                                |  |  |

| PC_ADD_5         | 50                                                           | I          | PCMCIA Address Bus Bit 5                                                                                                                                                                                                                                                                                                                                                |  |  |

| PC_ADD_6         | 49                                                           | I          | PCMCIA Address Bus Bit 6                                                                                                                                                                                                                                                                                                                                                |  |  |

| PC_ADD_7         | 48                                                           | I          | PCMCIA Address Bus Bit 7                                                                                                                                                                                                                                                                                                                                                |  |  |

| PC_ADD_8         | 47                                                           | I          | PCMCIA Address Bus Bit 8                                                                                                                                                                                                                                                                                                                                                |  |  |

| PC_ADD_9         | 46                                                           | I          | PCMCIA Address Bus Bit 9 (MSB)                                                                                                                                                                                                                                                                                                                                          |  |  |

| PC DATA BUS      |                                                              |            |                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| PC_DAT_0         | 70                                                           | I/O        | PCMCIA DATA Bus Bit 0 (LSB)                                                                                                                                                                                                                                                                                                                                             |  |  |

| PC_DAT_1         | 69                                                           | I/O        | PCMCIA DATA Bus Bit 1                                                                                                                                                                                                                                                                                                                                                   |  |  |

| PC_DAT_2         | 68                                                           | I/O        | PCMCIA DATA Bus Bit 2                                                                                                                                                                                                                                                                                                                                                   |  |  |

| PC_DAT_3         | 67                                                           | I/O        | PCMCIA DATA Bus Bit 3                                                                                                                                                                                                                                                                                                                                                   |  |  |

| PC_DAT_4         | 66                                                           | I/O        | PCMCIA DATA Bus Bit 4                                                                                                                                                                                                                                                                                                                                                   |  |  |

| PC_DAT_5         | 65                                                           | I/O        | PCMCIA DATA Bus Bit 5                                                                                                                                                                                                                                                                                                                                                   |  |  |

| PC_DAT_6         | 64                                                           | I/O        | PCMCIA DATA Bus Bit 6                                                                                                                                                                                                                                                                                                                                                   |  |  |

| PC_DAT_7         | 63                                                           | I/O        | PCMCIA DATA Bus Bit 7 (MSB)                                                                                                                                                                                                                                                                                                                                             |  |  |

| PC CONTROL SIG   | -<br>SNALS                                                   |            |                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| PC_CE1           | 45                                                           | I Pull-up  | Chip-select. Active low.                                                                                                                                                                                                                                                                                                                                                |  |  |

| PC_WE            | 44                                                           | I Pull-up  | Memory Write Enable. Active low.                                                                                                                                                                                                                                                                                                                                        |  |  |

| PC_OE            | 43                                                           | I Pull-up  | Memory Output Enable. Active low.                                                                                                                                                                                                                                                                                                                                       |  |  |

| PC_IOWR          | 42                                                           | I Pull-up  | I/O Write Enable. Active low.                                                                                                                                                                                                                                                                                                                                           |  |  |

| PC_IORD          | 41                                                           | I Pull-up  | I/O Read Enable. Active low.                                                                                                                                                                                                                                                                                                                                            |  |  |

| PC_REG           | 40                                                           | I Pull-up  | Common (1) or Attribute (0) Memory Indicator                                                                                                                                                                                                                                                                                                                            |  |  |

| PC_RESET         | 39                                                           | I, Trigger | Hard Reset. Active high.                                                                                                                                                                                                                                                                                                                                                |  |  |

| PC_INPACK        | 60                                                           | 0          | I/O Read Indicator (0 indicates that an I/O read access is being performed)                                                                                                                                                                                                                                                                                             |  |  |

| PC_WAIT          | 59                                                           | 0          | Wait Signal. Active low.                                                                                                                                                                                                                                                                                                                                                |  |  |

| PC_RDY           | 58                                                           | 0          | Ready/Interrupt Active Low :<br>In all modes, indicates when low that the circuit Is under initialization (CIS being<br>read or written). If no EEPROM is connected, PC_RDY remains low after reset<br>until the MCU writes something in the PROGN register.<br>In I/O modes <sup>(2)</sup> , transmits the interrupt coming from the UART, the I/O port or the<br>RAM. |  |  |

| PC_BVD1          | 57                                                           | 0          | In memory modes : always 1.<br>In I/O modes : if RINGEN = 1, reproduces UART_RI.<br>if RINGEN = 0, always 1.                                                                                                                                                                                                                                                            |  |  |

| PC_BVD2          | 56                                                           | 0          | In memory modes : always 1.<br>In I/O modes : if AUDIO = 1, reproduces SPKRIN.<br>if AUDIO = 0, always 1.                                                                                                                                                                                                                                                               |  |  |

## **II - PIN DESCRIPTION**

| II - PIN DESCRIPTION |      |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|----------------------|------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name                 | Pin  | Туре                  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| MCU ADDRESS B        | US   |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| MCU_ADD_0            | 9    | I                     | MCU Address Bus Bit 0 (LSB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| MCU_ADD_1            | 10   | I                     | MCU Address Bus Bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| MCU_ADD_2            | 11   | I                     | MCU Address Bus Bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| MCU_ADD_3            | 12   | I                     | MCU Address Bus Bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| MCU_ADD_4            | 13   | I                     | MCU Address Bus Bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| MCU_ADD_5            | 14   | I                     | MCU Address Bus Bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| MCU_ADD_6            | 15   | Ι                     | MCU Address Bus Bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| MCU_ADD_7            | 16   | I                     | MCU Address Bus Bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| MCU_ADD_8            | 17   | I                     | MCU Address Bus Bit 8 (MSB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| MCU - I/O - MEMC     | RYEX | TENSION D             | ATA BUS <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| MCU_DAT_0            | 78   | I/O                   | MCU, I/O or Memory Extension Data Bus Bit 0 (LSB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| MCU_DAT_1            | 77   | I/O                   | MCU, I/O or Memory Extension Data Bus Bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| MCU_DAT_2            | 76   | I/O                   | MCU, I/O or Memory Extension Data Bus Bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| MCU_DAT_3            | 75   | I/O                   | MCU, I/O or Memory Extension Data Bus Bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| MCU_DAT_4            | 74   | I/O                   | MCU, I/O or Memory Extension Data Bus Bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| MCU_DAT_5            | 73   | I/O                   | MCU, I/O or Memory Extension Data Bus Bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| MCU_DAT_6            | 72   | I/O                   | MCU, I/O or Memory Extension Data Bus Bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| MCU_DAT_7            | 71   | I/O                   | MCU, I/O or Memory Extension Data Bus Bit 7 (MSB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| MCU - I/O - MEMC     | RYEX | TENSION C             | ONTROL SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| MCU_CS               | 18   | I                     | Chip Select. Active low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| MCU_DSRD             | 19   | I                     | Data Strobe or Read Enable, depending on MCU_MOTEL (active low)                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| MCU_RWWR             | 20   | I                     | Read-Write or Write Enable, depending on MCU_MOTEL (active low)                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| MCU_MOTEL            | 24   | I                     | Motorola (1) or Intel (0) Like Bus Style                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| MCU_ACKWAIT          | 6    | O open collector      | Wait or Acknowledge depending on MCU-MOTEL (active low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| CSL_ALE              | 7    | I/O                   | In memory extension mode : output, active low. Indicates (when 0) an access to the memory extension.<br>In I/O extension mode : output, active low. Indicates (when 0) that the I/O port address has been recognized.<br>In other modes : address latch enable input active high. It is used when the MCU data bus is multiplexed to validate the 8 lsb's of the address on MCU_DAT. The address is latched inside the circuit when CSL_ALE goes low. When the MCU bus is not multiplexed, CSL_ALE must be connected to 0. |  |

| MCU_IRQ              | 8    | I/O open<br>collector | In memory extension mode : output, not used.<br>In I/O extension mode : interrupt input active low, transmitted to the PC on the<br>PC_RDY pin.<br>In other modes : interrupt output towards the MCU, active low.                                                                                                                                                                                                                                                                                                          |  |

| IOW                  | 4    | 0                     | In memory extension mode : reproduces PC_WE.<br>In I/O extension mode, reproduces PC_IOW when the I/O port address is<br>recognized (otherwise takes value 1).<br>In other modes : remains at 1.                                                                                                                                                                                                                                                                                                                           |  |

| IOR                  | 5    | 0                     | In memory extension mode : reproduces PC_OE.<br>In I/O extension mode, reproduces PC_IOR when the I/O port address is<br>recognized (otherwise takes value 1).<br>In other modes : remains at 1.                                                                                                                                                                                                                                                                                                                           |  |

## **II - PIN DESCRIPTION**

| Name                       | Pin   | Туре      | Function                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------|-------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JART RELATED F             |       | 1960      |                                                                                                                                                                                                                                                                                                                                                                           |

| UART_RI                    | 25    | I         | Ring Input : can be reproduced on PC BVD1                                                                                                                                                                                                                                                                                                                                 |

| UART_SIN                   | 26    | -         | Serial Input                                                                                                                                                                                                                                                                                                                                                              |

| UART_SOUT                  | 27    | 0         | Serial Output                                                                                                                                                                                                                                                                                                                                                             |

| UART_DCD                   | 28    |           | Data Carrier Detect                                                                                                                                                                                                                                                                                                                                                       |

| UART CTS                   | 29    |           | Clear To Send                                                                                                                                                                                                                                                                                                                                                             |

| UART_DSR                   | 30    |           | Data Set Ready                                                                                                                                                                                                                                                                                                                                                            |

| UART_RTS                   | 31    | 0         | Request To Send                                                                                                                                                                                                                                                                                                                                                           |

| UART DTR                   | 32    | 0         | Data Terminal Ready                                                                                                                                                                                                                                                                                                                                                       |

| BAUDOUT                    | 33    | 0         | UART Transmit Clock                                                                                                                                                                                                                                                                                                                                                       |

| RCLK                       | 34    | I         | Receive Clock for the UART                                                                                                                                                                                                                                                                                                                                                |

| SERVICE PORTS              | 1     |           | ,                                                                                                                                                                                                                                                                                                                                                                         |

| INIT                       | 23    | 0         | Initialization signal provided by the chip for use on the PCMCIA card. It is active high when the card receives a hard or a soft reset.                                                                                                                                                                                                                                   |

| PWRDWN                     | 22    | 0         | Reproduces Bit PWRDWN of Register R1. active high.                                                                                                                                                                                                                                                                                                                        |

| LOCK_ON                    | 21    | Ι         | Two consecutive rising transitions on this signal put the chip in stand-by :<br>CLKOUT receives MCU_DIV output instead of the internal clock, unless between<br>these two transitions, stand-by procedure is cancelled. Stand-by procedure is<br>cancelled when any of UART_RI or UART_SOUT goes low, or when any of<br>PWRDWN or PC_RESET goes high.                     |

| CLKIN                      | 35    | I         | Alternate Clock Input. (possibly delivered by a data-pump modem). It is either this clock (when Bit 3 of PROGN register is '1'), or the internal oscillator clock (when Bit 3 of PROGN register is '0') which will be used by UART_DIV to produce the CLOCK for the internal UART.                                                                                        |

| CLKOUT                     | 3     | 0         | Output Clock Available for a MCU. It is either the internal oscillator clock, or the clock coming from MCU_DIV in stand-by mode when it is desired to reduce the MCU's power consumption.                                                                                                                                                                                 |

| XTIN                       | 2     | I         | Oscillator Input. Can be connected either on an external quartz to use the internal oscillator, or on an external oscillator output. The clock on this pin is the one which is used internally by the circuit to operate its internal logic and state machines. The clock used by the UART can come from XTIN or from CLKIN after a division to get the proper frequency. |

| XTOUT                      | 1     | 0         | Internal Oscillator Output. When the internal oscillator is used, to be connected on the other pin of the quartz crystal.                                                                                                                                                                                                                                                 |

| SPKRIN                     | 36    | Ι         | Speaker Input. This input can be reproduced on PC_BVD2 output in I/O mode when AUDIO Bit is one.                                                                                                                                                                                                                                                                          |

| <sup>2</sup> C LINE (PORTS | RELAT | ED TO THE | EXTERNAL EEPROM)                                                                                                                                                                                                                                                                                                                                                          |

| SDA | 37 | I/O open<br>collector | I <sup>2</sup> C Bus Data Line. An external pull-up resistor is mandatory on this pin.                                                                                                                          |

|-----|----|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCL | 38 | I/O open<br>collector | $\rm I^2C$ Bus Clock Line. Although this pin is inout, the circuit only uses this Pin as an out Pin. For this reason, one cannot modify the $\rm I^2C$ line frequency by forcing SCL low from outside the chip. |

Notes: 1. Memory mode : mode for which, depending on the value of bits UE, MODE0, MODE1 in R0 register, only common or attribute memory accesses are allowed (i.e., no I/O access is allowed).

I/O mode : mode for which, depending on the value of bits UE, MODE0, MODE1 in R0 register, only attribute memory and I/O accesses are allowed (i.e., no common memory access is allowed).

A number of pins can be used in different ways either to connect a MCU or to connect a memory extension or an I/O

extension. These pins are MCU\_DAT[7..0], MCU\_IRQ, CSL\_ALE, IOW and IOR. This corresponds to three different

behaviours for the circuit.

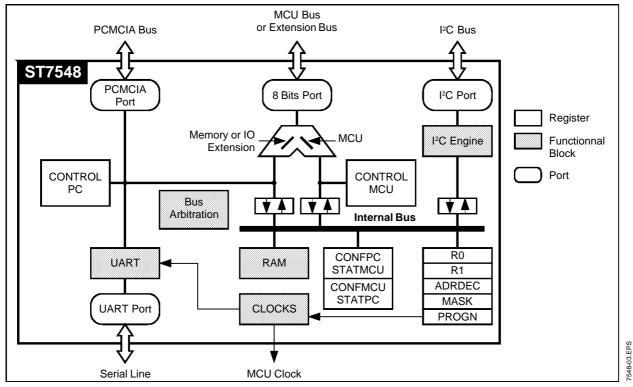

#### **III - BLOCK DIAGRAMS**

The here under schematic shows the main functions and data flows of the chip.

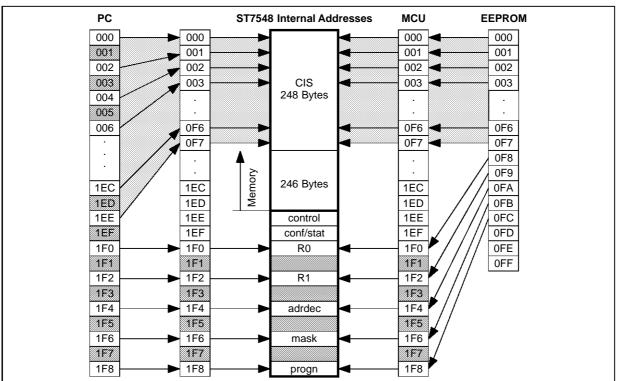

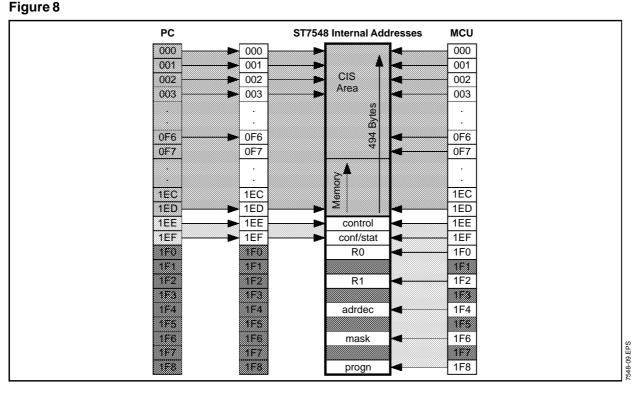

The CIS (Card Information Structure in PCMCIA terminology) is a memory and registers area which describes the PCMCIA card configuration. During chip initialization, it is loaded from an external EEPROM through the  $l^2$ C channel (this is the normal behaviour when such a memory is present) or from the MCU (if no E2PROM is connected; in this case, loading the CIS is under the MCU's responsibility).

The RAM allows high speed transfers between the PC and the MCU.

The UART may exchange informations with another compatible UART.

When no MCU is necessary, it is possible to connect instead a peripheral requiring an 8 bits parallel interface, or an 8 bits memory extension. There is only one set of ports for the MCU, the peripheral and the memory extension. Therefore, only one of them may be connected at a time on the chip.

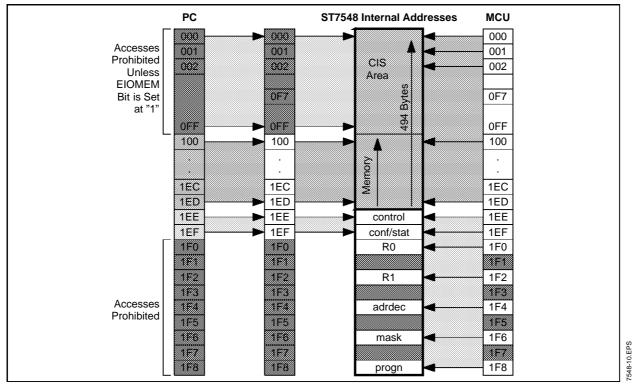

After reset, the RAM memory contains the CIS (loaded from the EEPROM through the I<sup>2</sup>C bus, or by the MCU). The RAM is also used to exchange information between the PC and the MCU. Its capacity is 494 bytes (hexadecimal addresses ranging from x"000" to x"1ED"). It is organized in such a way that the CIS does not take all the available room. Thus it is possible to perform exchanges between the PC and the MCU while keeping the CIS available for read.

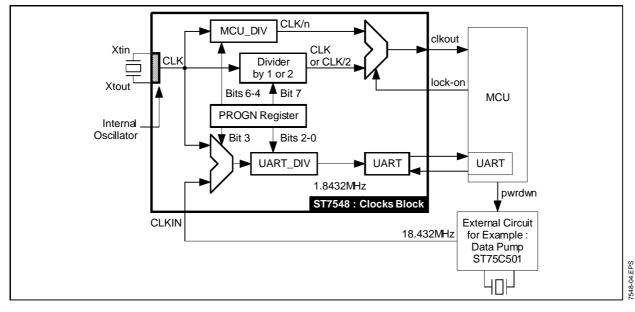

The clocks block produces the necessary clock signals. It contains multiplexers and frequency dividers which can be programmed with the PROGN register. With its internal oscillator, it delivers the external clock CLKOUT which can be used to drive a MCU. It provides the UART with the required clock, building it either from the internal oscillator, or from the external clock input CLKIN. It incorporates programmable dividers which allow to adapt the different clock frequencies.

The registers are used to configurate the chip and to synchronise data transfer between the PC and the MCU.

The circuit considers that they are three masters : the PCMCIA, the MCU and the I<sup>2</sup>C interfaces. The registers and the memory can be reached by the masters. The table in paragraph IV.11 "ADDRESS-ING CAPABILITIES TABLE" shows the access permission. Each device which is supposed to be reached by at least two masters is placed on a common internal bus. An arbitration logic manages the resulting access conflicts. For this reason, accessing one of the registers or memory placed on the common bus makes the related master support WAIT cycles.

The addresses are given in the table. Two elements can be placed at variable addresses : the UART and the I/O port. For the first one, the address is defined in the R0 register ; for the second one, it is defined in the ADRDEC register, and the recognized address field width is defined in the MASK register.

7548-02.EPS

ST7548 MCU RAM CIS or **PCMCIA** PERIPHERAL Socket or MEMORY I<sup>2</sup>C UART **EXTENSION** EEPROM UART **PCMCIA Card**

SGS-THOMSON

Figure 1 : Simplified Block Diagram of the Data Flows Allowed by the Chip

# III - BLOCK DIAGRAMS (continued)

Figure 2 : Chip Block Diagram

# **IV - FUNCTIONNAL DESCRIPTION**

## **IV.1 - PCMCIA ADDRESSING MODES**

Through a PCMCIA port, a computer may perform its accesses in three different modes : the common memory mode, the attribute memory mode, and the I/O mode.

The usual addressing mode for memory is common memory mode. The PC\_REG signal is '1', and the PC\_OE and PC\_WE signals are used as read/write signals.

The attribute memory mode is mainly used to read configuration information (in registers or memory) of the PCMCIA cards. It differs from the common memory mode in that the PC\_REG signal is '0'.

The I/O mode is used to access I/O ports. In this case, the PC\_REG is '0' and the read/write signals are PC\_IORD and PC\_IOWR. The I/O mode allows interrupts to be transmitted to the PCMCIA port. That is why, in the ST7548, the I/O mode can be

used not only to access the I/O port, but also to access the memory, thus allowing to synchronize data transfer between the MCU and the PC using interrupts.

In the ST7548, from the PC (or PCMCIA) point of view, there are registers, a memory, an UART, an I/O port and a memory extension port. Each of them cannot be addressed in any mode. For example, the UART and the I/O port can be addressed only in I/O mode. The table in paragraph IV.11 "AD-DRESSING CAPABILITIES TABLE" shows in the PCMCIA columns under which conditions the PCMCIA port accesses the different blocks in the circuit, and when the circuit generates a wait state to the PCMCIA interface. It also shows what can be addressed by the MCU (and if a WAIT is sent to the MCU), and what can be reached by the I<sup>2</sup>C channel.

#### IV.2 - CLOCKS (Figure 3)

#### Introduction

The circuit includes an oscillator (XTIN and XTOUT pins) which has been tuned for frequencies ranging from 12 to 24MHz. This oscillator requires an external quartz crystal. It is also possible to operate the circuit at frequencies outside this range, but in this case a quartz crystal cannot be used : an external oscillator must deliver the desired frequency on the XTIN pin. Regardless of its origin, the clock present on XTIN becomes internally CLK, the basic clock of the ST7548. CLK is also named "internal oscillator clock". It is used to operate the internal logic of the chip (state machines and others).

The circuit delivers the CLKOUT clock which relies on the internal oscillator clock. CLKOUT can be used as the basic clock for an MCU placed outside the ST7548. In stand-by, CLKOUT can be slowed down owing to the "MCU\_DIV" divider.

The on-chip UART receives the clock which goes out of the frequency divider named "UART\_DIV". The input of this divider is either the internal oscillator clock or an external clock connected on CLKIN pin. The division ratios in UART\_DIV are well suited to the following clock frequencies : 3.6864MHz, 7.3728MHz, 14.7456MHz, 18.432MHz, 22.1184MHz, 29.4912MHz, 33.1776MHz, 36.864MHz.

The clocks operate in three different ways : normal behaviour, stand-by, and power down.

#### **Normal Behaviour**

After reset is released, the clocks run freely, and it is the internal oscillator clock that is sent on UART\_DIV. Then, depending on the content of PROGN register bit 3, the UART clock may come from CLK or CLKIN divided in UART\_DIV.

The MCU\_DIV divider is not used : the multiplexer which follows and delivers CLKOUT uses the CLK or CLK/2 input. Thus, on CLKOUT, it is CLK/2 which is issued when PROGN register bit 7 is '0' (default value), and CLK when this bit is '1'.

#### Stand-by

What is desired in this mode, is to temporarily reduce the PCMCIA card power consumption, but the card remains able to become operational again at any moment. Putting the card in stand-by depends upon a MCU action. For this, it sends two consecutive rising edges on the LOCK\_ON pin. Doing this causes MCU\_DIV to become active. This divider then takes into account the division ratio indicated in the PROGN register. The frequency delivered on CLKOUT is then a sub-multiple of CLK. A PC\_RE-SET (active high) or one of the UART signals UART\_RI, UART\_SOUT at '0' wake up the circuit and put it back in normal mode. In the same way, if one of these signals occurs between the two rising edges on LOCK\_ON, the stand-by procedure is cancelled.

Depending upon the way that the circuit is used (use in conjunction with a 75C501 data pump for example), the MCU may also stop the 75C501. In this case, the 18.432MHz frequency is no longer delivered on CLKIN, and the UART is stopped, unless the user links the UART\_DIV input to the local oscillator (by programming accordingly the PROGN register). Switching between CLKIN and the local oscillator clock is done in such a way that no glitch nor shortened cycle happens. The counterpart is that the clock cycle may temporarily be longer.

#### Waking up After a Stand-by

The circuit goes out of stand-by if a reset happens or if at least one of the UART signals UART\_RI or UART\_SOUT becomes '0' or if PWRDWN becomes '1'.

If the PC wants to wake up the circuit, it can do it with the UART, simply sending a byte to it.

#### **Powerdown Mode**

In this mode, the user doesn't intend to use the PCMCIA card on which the circuit is placed. So it is not the UART that will wake it up.

The circuit is placed in powerdown under the PC's responsibility. The PC writes a '1' in R1 register PWRDWN bit. The circuit then no longer delivers any clock neither on CLKOUT nor on the UART, and is no longer able to perform accesses to any-thing else than the R0 and R1 registers. The circuit will only restart after the PC has written a '0' in the PWRDWN bit.

Figure 3 : Theoretical Schematic

#### IV.3 - UART

The UART is fully compatible with a 16C450 UART. It also provides a transmit and receive FIFO as in a 16C550 UART (see Chapter X.3). Please refer to the documentation on this type of UART to have a detailed description of its behaviour.

The UART may only be used when the UE bit (Uart Enable) in register R0 is set to '1'. The UART address can be chosen between four values depending on the content of R0 register. The three LSB's of the PCMCIA address bus are transmitted to the UART : they are used to select the internal UART registers. The UART thus covers an 8 bytes address range.

The clock which enters the UART is divided by the value held in DLM and DLL UART registers to produce the NBAUD signal. The most common frequency for the UART clock is 1.8432MHz. The table below shows the required divisor value in DLM-DLL to generate typical baud rates for a set of input frequencies (Table 2).

After reset, DLL and DLM are undefined. They are not affected by reset.

| Table 1 | : UART | Registers |

|---------|--------|-----------|

|---------|--------|-----------|

| Address (Note 1) | DLAB (Note 2) | Register Name                    | Comment            |

|------------------|---------------|----------------------------------|--------------------|

| 0                | 0             | RBR Receiver Buffer Register     | Read only          |

| 0                | 0             | THR Transmitter Holding Register | Write only         |

| 1                | 0             | IER Interrupt Enable Register    |                    |

| 2                | Х             | IIR Interrupt Ident Register     | Read only          |

| 2                | Х             | FCR Fifo Control Register        | Write only         |

| 3                | Х             | LCR Line Control Register        |                    |

| 4                | Х             | MCR Modem Control Register       |                    |

| 5                | Х             | LSR Line Status Register         | Read only (Note 3) |

| 6                | Х             | MSR Modem Status Register        |                    |

| 7                | Х             | SCR Scratch Register             |                    |

| 0                | 1             | DLL Divisor Latch (LSB)          |                    |

| 1                | 1             | DLM Divisor Latch (MSB)          |                    |

Notes: 1. The address given in this column refers to the 3 LSBs of the PCMCIA address bus. The complete address of a register is obtained by adding the indicated address and the one of the COM port as defined in the R0 register.

2. DLAB is bit 7 of the UART\_LCR register.

3. This register is intended to be read only during normal operation and written during production testing.

#### Table 2

| Line Baud Rate | NBAUD<br>Frequency | UART Clock =<br>1.8432MHz | UART Clock =<br>3.072MHz | UART Clock =<br>8.00MHz (Note 1) |

|----------------|--------------------|---------------------------|--------------------------|----------------------------------|

| 50             | 800                | 2304                      | 3840                     | 10000                            |

| 75             | 1200               | 1536                      | 2560                     | 6667                             |

| 110            | 1760               | 1047                      | 1745                     | 4545                             |

| 134.5          | 2152               | 857                       | 1428                     | 3717                             |

| 150            | 2400               | 768                       | 1280                     | 3333                             |

| 300            | 4800               | 384                       | 640                      | 1667                             |

| 600            | 9600               | 192                       | 320                      | 833                              |

| 1200           | 19200              | 96                        | 160                      | 417                              |

| 1800           | 28800              | 64                        | 107                      | 278                              |

| 2000           | 32000              | 58                        | 96                       | 250                              |

| 2400           | 38400              | 48                        | 80                       | 208                              |

| 3600           | 57600              | 32                        | 53                       | 139                              |

| 4800           | 76800              | 24                        | 40                       | 104                              |

| 7200           | 115200             | 16                        | 27                       | 69                               |

| 9600           | 153600             | 12                        | 20                       | 52                               |

| 19200          | 307200             | 6                         | 10                       | 26                               |

| 38400          | 614400             | 3                         | 5                        | 13                               |

| 56000          | 896000             | 2                         | ** (Note 2)              | 9                                |

| 115200         | 1843200            | 1                         | **                       | **                               |

| 128000         | 2048000            | **                        | **                       | 4                                |

| 256000         | 4096000            | **                        | **                       | 2                                |

Notes: 1. In this column, most theoretical divisors are decimal numbers. They have been rounded to the nearest integer. 2. \*\* = No suitable divisor.

## IV.4 - I<sup>2</sup>C LINE INTERFACE

## **IV.4.1 - Introduction**

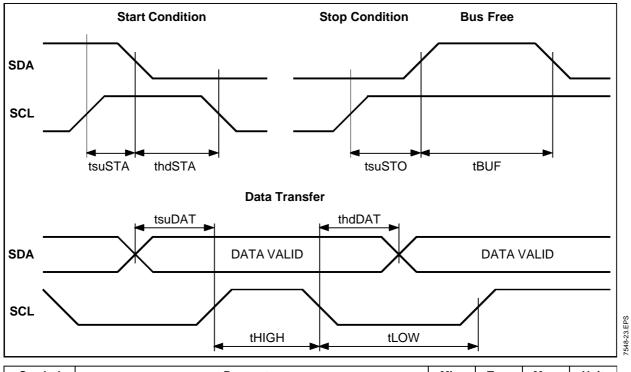

An  $I^2C$  line has two wires : the SDA wire carries serial data, the SCL wire carries the clock. It is used for a wide range of applications, including some EEPROMs. It allows several master and slave devices to exchange data while efficiently managing access conflicts. Each device present on the bus has a unique address. Data transfers, whatever their direction is, are always initialized by a master. The slave may slow down the clock if it finds it is too fast.

It is a simplified version of this line which is incorporated in the circuit. It doesn't manage accesses conflicts between several masters. In fact, the ST7548 will always be the only master on the line. The EEPROM is the slave. This is quite enough for the application area. The I<sup>2</sup>C line is managed by a state machine clocked by the internal oscillator

clock. The EEPROM must be wired at address 0. The recommended model is a ST24C02A or compatible.

#### IV.4.2 - State Machine Behaviour

The line is managed by a state machine. After a hard or soft reset, the state machine will try and read an EEPROM using the "Sequential Random Read" protocol. If it doesn't get any answer, there is no EEPROM, and it stops.

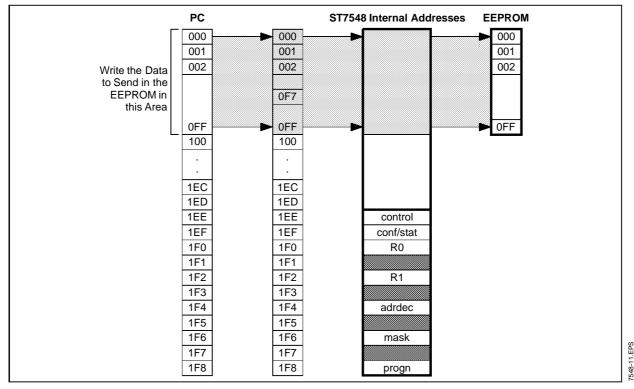

The PC may also ask the ST7548 to copy in the EEPROM data that have previously been placed in the RAM. It is a convenient way of working on the CIS. This operation is launched by writing a '1' in CONTROLPC register bit 7 (VALWREEPROM). The state machine puts this bit back to '0' when the dump is finished. The state machine uses the "Byte Write" protocol to transfer the data to the EEPROM.

#### **IV.4.3 - Sequential Random Read Protocol**

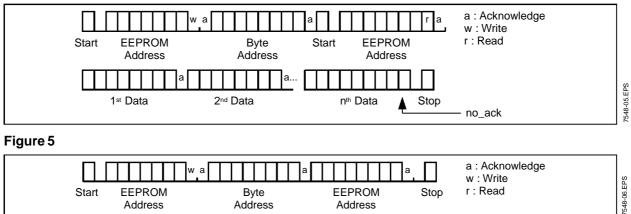

The state machine sends the device address (the EEPROM address on the I<sup>2</sup>C line), followed by the first byte address (an address inside the EEPROM). Then, it sends again the device address and reads the first byte, then the second, and so on, without sending any address again. The EEPROM internally performs address incrementing. When the state machine wants to stop reading, it doesn't acknowledge the last received byte and sends a STOP condition on the line (see Figure 4).

#### IV.4.4 - Byte Write Protocol

The state machine performs a complete write cycle for each byte, (sends the device address, the byte address, and the byte to write) and repeats this operation as long as there is something to write. The EEPROM may take some time to physically write the data, and hence, not be ready when the next data comes. In this case, it answers no acknowledge after it has received the device address. The state machine makes a polling on this signal (sends the device address until there is an acknowledge) to ensure that every byte will be writ-

Address

ten (see Figure 5).

The above sequence is repeated for each byte.

## **IV.5 - BUS ARBITRATION**

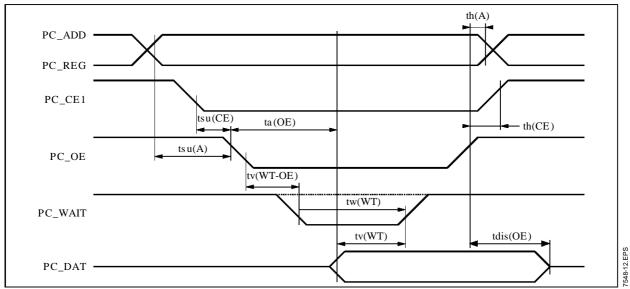

This block manages access conflicts which can occur during accesses requiring use of the internal bus. Its function is to register access requests, allow accesses and put in a wait state those that can't be satisfied immediately by sending them wait signals. It is controlled by a state machine which operates with the internal oscillator clock.

Between the MCU and the PCMCIA, if requests are sent at high speed, the access priority is switched after each access to prevent one of them from always taking the bus. When the I<sup>2</sup>C line requires access, it has absolute priority : when the CIS is being read or dumped, no bus access is possible for the MCU and the PCMCIA.

Each access to any register or RAM by a MO-TOROLA like MCU automatically produces a DTACK like wait signal on the MCU\_ACKWAIT pin, even if no bus arbitration took place.

#### Figure 4

Address

Address

## **IV.6 - REGISTERS**

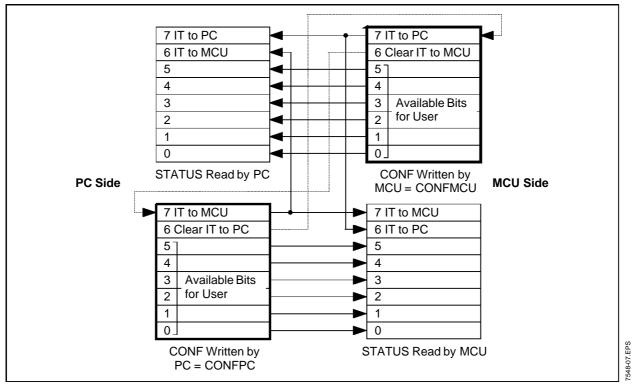

IV.6.1 - Control PC (8 bits, address x"1EE", R/W)

This register is only accessible from the PCMCIA side. Neither the MCU nor the  $I^2C$  line can reach it. After a hard or soft reset, the register has all bits at 0.

| Bit | Name                        | Action                                                                                                       |

|-----|-----------------------------|--------------------------------------------------------------------------------------------------------------|